Fetch, decode, execute cycle скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Fetch, decode, execute cycle в качестве 4k

У нас вы можете посмотреть бесплатно Fetch, decode, execute cycle или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Fetch, decode, execute cycle в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Fetch, decode, execute cycle

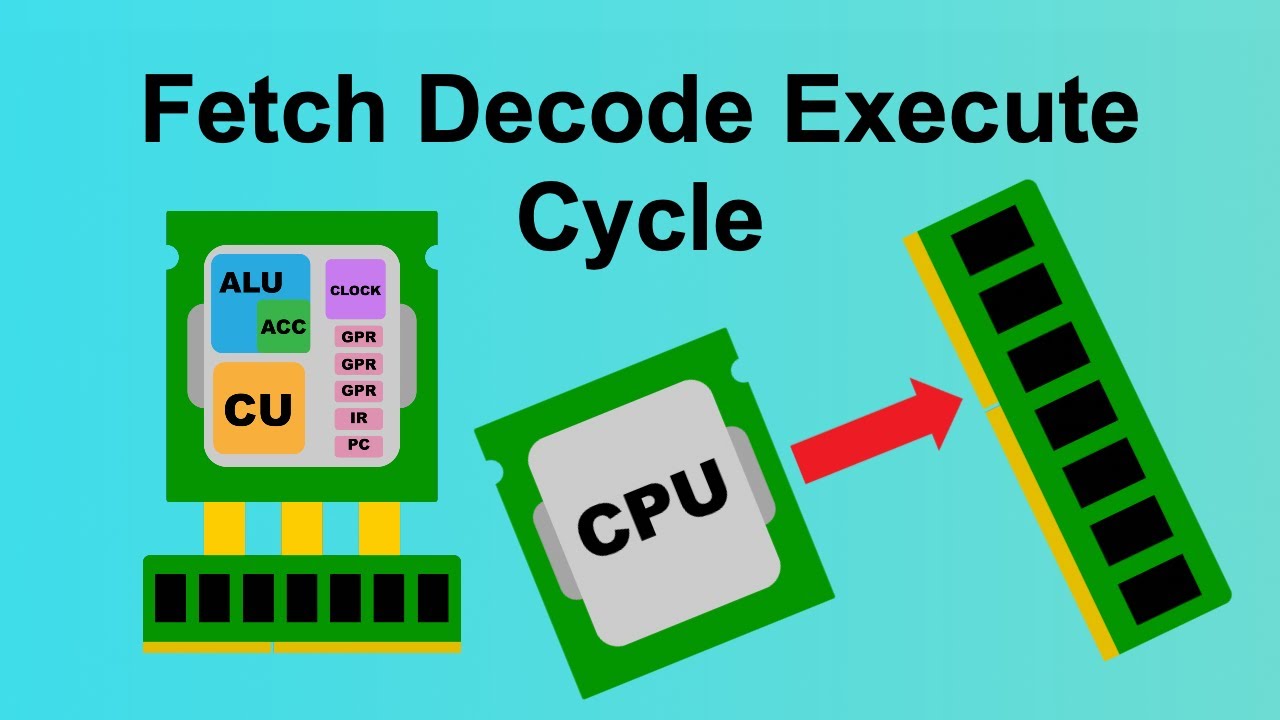

0:01Skip to 0 minutes and 1 secondNow let’s look at how the CPU can perform calculations using a process known as the fetch, decode, execute cycle. 0:13Skip to 0 minutes and 13 secondsHere we have a representation of a CPU and RAM. The registers are also shown, where data can be temporarily stored. The program counter starts at 0000. This means that the first address in RAM that the computer will look for an instruction is at 0000. The computer needs somewhere to store the current address in RAM that it is looking for. This is what the memory address register is for. 0000 is therefore copied into the MAR. A signal is then sent down to the address bus, to the RAM. The control unit sends out a memory read signal and the contents of the address 0000 are copied through the data bus to the memory data register. 0:59Skip to 0 minutes and 59 secondsAs the contents of address 0000 is an instruction, it is copied into the instruction register. As our first instruction has been fetched, the system is at the end of the fetch stage of the cycle. The program counter can be incremented by one so the system is ready to read the next instruction. 1:22Skip to 1 minute and 22 secondsNow the instruction needs to be decoded. It is sent via the data bus to the control unit. Here, the data is split into two sections. There is the operation code, or op code, which in this example is the first four bits. This is the command that the computer will carry out. The second four bits of the operand. This is the address in RAM where the data to be operated on is stored. The control unit can translate op code into instructions, so here, the control unit translates the op code 0101 into a load from RAM instruction. 2:07Skip to 2 minutes and 7 secondsNow the command will be executed. The operand is copied to the MAR as this is the address of the data that needs to be loaded. The data address 0100 is then fetched from RAM and then passed up the data bus to the MDR. As it is not an instruction but simply data, it is then passed to the accumulator. This is a complete fetch, decode, execute cycle. We’ll run through the next cycle a little faster so that you can see the entire program being executed. The instruction op codes and address operand is placed in the IR and the PC increase by one again. 2:44Skip to 2 minutes and 44 secondsNow the instruction is decoded while the address of the data to be acted on is placed in the MAR. 2:54Skip to 2 minutes and 54 secondsThe new data is fetched from the address and eventually ends up in the accumulator, along with the results of the previous cycle. To finish off this stage, the two values in the accumulator are passed in through the ALU, where they can be added together as was instructed by the op code. The results are then placed back into the accumulator. So that’s a second cycle complete. The last cycle is for the instruction at 0010. It uses the op code 0011, which is store, and the operand 0110, which is the last address in the RAM shown. So this cycle takes the results of the addition in the accumulator and stores it back into RAM. Share, Support, Subscribe!!! Subscribe: / @senior.professor473 gaming channel : / @frontlinegamerswolf2529 Twitter: / wolffrontline Facebook Myself: https://www.facebook.com/profile.php?... Instagram: / frontlinegamerswolf Business Email : BROARENAAMERICAN123@gmail.com