Настройка компиляции и режим симуляции FPGA CompactRIO скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Настройка компиляции и режим симуляции FPGA CompactRIO в качестве 4k

У нас вы можете посмотреть бесплатно Настройка компиляции и режим симуляции FPGA CompactRIO или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Настройка компиляции и режим симуляции FPGA CompactRIO в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

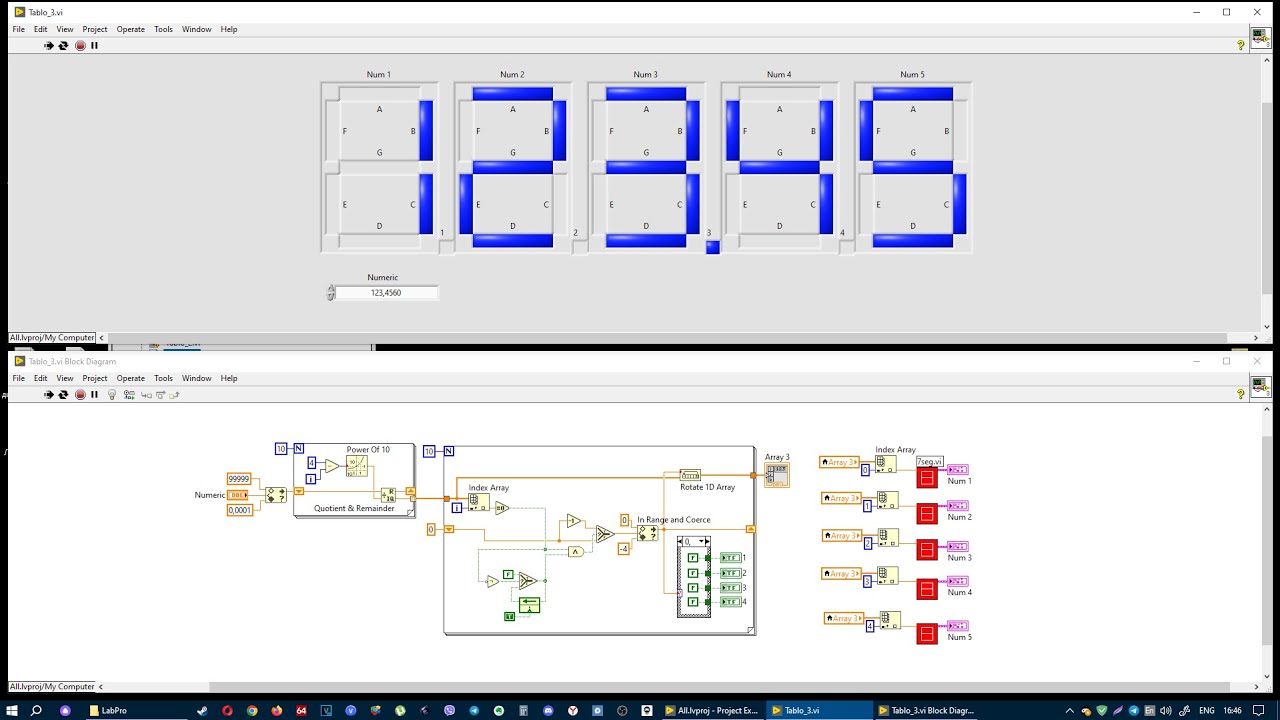

Настройка компиляции и режим симуляции FPGA CompactRIO

Режим симуляции для отладки низкоуровневой программы FPGA / LabVIEW. Desktop Execution Node. Simulation mode Chassis/FPGA Target 0:00 Введение 2:20 Установка пакетов 6:05 Настройка модулей расширения 8:50 VI FPGA 11:30 Результаты компиляции 12:48 Пример программы 15:00 Режим симуляции 20:10 Типы данных 29:20 Примеры симуляций 43:50 Компиляция 46:20 Управляющая TOP VI