–ú–æ–¥—É–ª—å ‚Ññ 3: –£–º–Ω–æ–∂–∏—Ç–µ–ª—å DSP | –°–∏—Å—Ç–µ–º–∞ Verilog —Å–∫–∞—á–∞—Ç—å –≤ —Ö–æ—Ä–æ—à–µ–º –∫–∞—á–µ—Å—Ç–≤–µ

–ü–æ–≤—Ç–æ—Ä—è–µ–º –ø–æ–ø—ã—Ç–∫—É...

–°–∫–∞—á–∞—Ç—å –≤–∏–¥–µ–æ —Å —é—Ç—É–± –ø–æ —Å—Å—ã–ª–∫–µ –∏–ª–∏ —Å–º–æ—Ç—Ä–µ—Ç—å –±–µ–∑ –±–ª–æ–∫–∏—Ä–æ–≤–æ–∫ –Ω–∞ —Å–∞–π—Ç–µ: –ú–æ–¥—É–ª—å ‚Ññ 3: –£–º–Ω–æ–∂–∏—Ç–µ–ª—å DSP | –°–∏—Å—Ç–µ–º–∞ Verilog –≤ –∫–∞—á–µ—Å—Ç–≤–µ 4k

–£ –Ω–∞—Å –≤—ã –º–æ–∂–µ—Ç–µ –ø–æ—Å–º–æ—Ç—Ä–µ—Ç—å –±–µ—Å–ø–ª–∞—Ç–Ω–æ –ú–æ–¥—É–ª—å ‚Ññ 3: –£–º–Ω–æ–∂–∏—Ç–µ–ª—å DSP | –°–∏—Å—Ç–µ–º–∞ Verilog –∏–ª–∏ —Å–∫–∞—á–∞—Ç—å –≤ –º–∞–∫—Å–∏–º–∞–ª—å–Ω–æ–º –¥–æ—Å—Ç—É–ø–Ω–æ–º –∫–∞—á–µ—Å—Ç–≤–µ, –≤–∏–¥–µ–æ –∫–æ—Ç–æ—Ä–æ–µ –±—ã–ª–æ –∑–∞–≥—Ä—É–∂–µ–Ω–æ –Ω–∞ —é—Ç—É–±. –î–ª—è –∑–∞–≥—Ä—É–∑–∫–∏ –≤—ã–±–µ—Ä–∏—Ç–µ –≤–∞—Ä–∏–∞–Ω—Ç –∏–∑ —Ñ–æ—Ä–º—ã –Ω–∏–∂–µ:

-

–ò–Ω—Ñ–æ—Ä–º–∞—Ü–∏—è –ø–æ –∑–∞–≥—Ä—É–∑–∫–µ:

–°–∫–∞—á–∞—Ç—å mp3 —Å —é—Ç—É–±–∞ –æ—Ç–¥–µ–ª—å–Ω—ã–º —Ñ–∞–π–ª–æ–º. –ë–µ—Å–ø–ª–∞—Ç–Ω—ã–π —Ä–∏–Ω–≥—Ç–æ–Ω –ú–æ–¥—É–ª—å ‚Ññ 3: –£–º–Ω–æ–∂–∏—Ç–µ–ª—å DSP | –°–∏—Å—Ç–µ–º–∞ Verilog –≤ —Ñ–æ—Ä–º–∞—Ç–µ MP3:

–ï—Å–ª–∏ –∫–Ω–æ–ø–∫–∏ —Å–∫–∞—á–∏–≤–∞–Ω–∏—è –Ω–µ

–∑–∞–≥—Ä—É–∑–∏–ª–∏—Å—å

–ù–ê–ñ–ú–ò–¢–ï –ó–î–ï–°–¨ –∏–ª–∏ –æ–±–Ω–æ–≤–∏—Ç–µ —Å—Ç—Ä–∞–Ω–∏—Ü—É

–ï—Å–ª–∏ –≤–æ–∑–Ω–∏–∫–∞—é—Ç –ø—Ä–æ–±–ª–µ–º—ã —Å–æ —Å–∫–∞—á–∏–≤–∞–Ω–∏–µ–º –≤–∏–¥–µ–æ, –ø–æ–∂–∞–ª—É–π—Å—Ç–∞ –Ω–∞–ø–∏—à–∏—Ç–µ –≤ –ø–æ–¥–¥–µ—Ä–∂–∫—É –ø–æ –∞–¥—Ä–µ—Å—É –≤–Ω–∏–∑—É

—Å—Ç—Ä–∞–Ω–∏—Ü—ã.

–°–ø–∞—Å–∏–±–æ –∑–∞ –∏—Å–ø–æ–ª—å–∑–æ–≤–∞–Ω–∏–µ —Å–µ—Ä–≤–∏—Å–∞ ClipSaver.ru

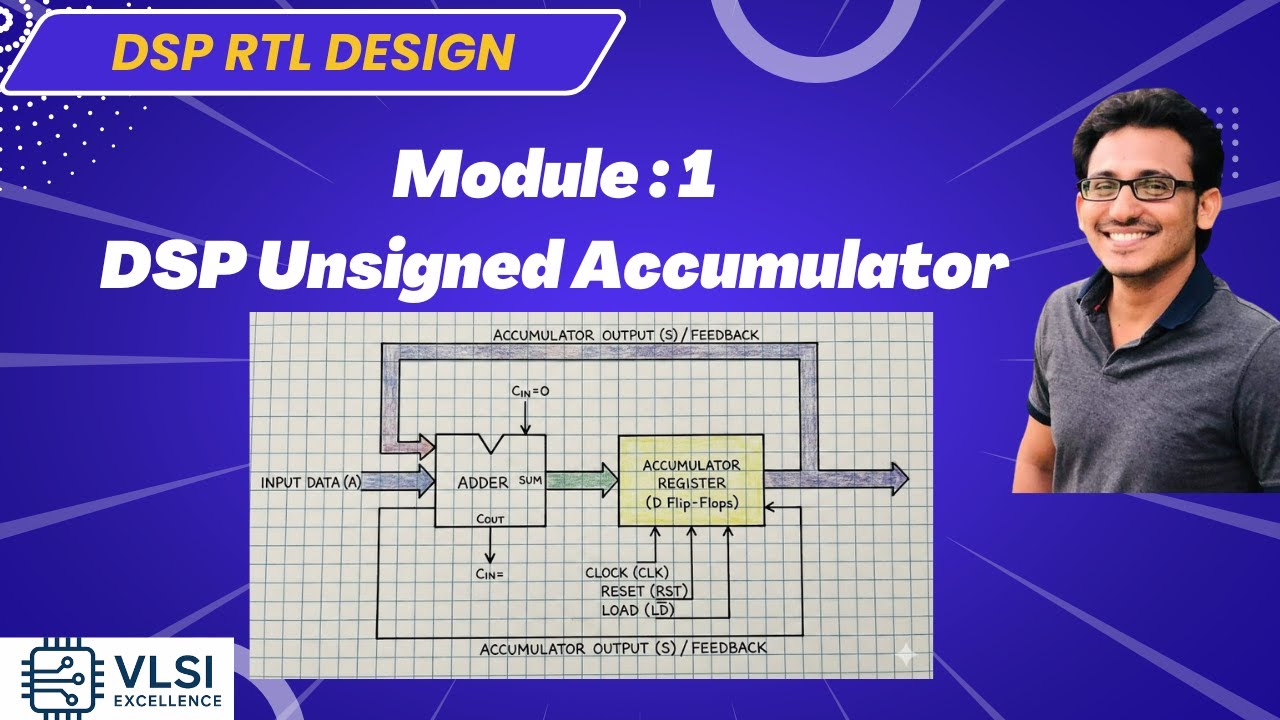

–ú–æ–¥—É–ª—å ‚Ññ 3: –£–º–Ω–æ–∂–∏—Ç–µ–ª—å DSP | –°–∏—Å—Ç–µ–º–∞ Verilog

–û—Å–æ–±–µ–Ω–Ω–æ—Å—Ç–∏: 1) –ö–æ—Ä—Ä–µ–∫—Ç–Ω–∞—è –æ–±—Ä–∞–±–æ—Ç–∫–∞ –∑–Ω–∞–∫–æ–≤–æ–≥–æ –∏ –±–µ–∑–∑–Ω–∞–∫–æ–≤–æ–≥–æ —É–º–Ω–æ–∂–µ–Ω–∏—è 2) –ü–æ–ª–Ω–æ—Å—Ç—å—é —Å–∏–Ω—Ö—Ä–æ–Ω–Ω–∞—è –∫–æ–Ω—Å—Ç—Ä—É–∫—Ü–∏—è 3) –ü–∞—Ä–∞–º–µ—Ç—Ä–∏–∑–æ–≤–∞–Ω–Ω–∞—è —Ä–∞–∑—Ä—è–¥–Ω–æ—Å—Ç—å (–Ω–∞—Å—Ç—Ä–∞–∏–≤–∞–µ–º—ã–π —Ä–∞–∑–º–µ—Ä –æ–ø–µ—Ä–∞–Ω–¥–∞) 4) –≠—Ñ—Ñ–µ–∫—Ç–∏–≤–Ω–æ—Å—Ç—å –∞–ø–ø–∞—Ä–∞—Ç–Ω–æ–π —Ä–µ–∞–ª–∏–∑–∞—Ü–∏–∏ 5) –ß–∏—Å—Ç—ã–π –¥–≤—É—Ö—Å—Ç—É–ø–µ–Ω—á–∞—Ç—ã–π –∫–æ–Ω–≤–µ–π–µ—Ä: –∏–∑–≤–ª–µ—á–µ–Ω–∏–µ –∞–º–ø–ª–∏—Ç—É–¥—ã + —É–º–Ω–æ–∂–µ–Ω–∏–µ + –∫–æ—Ä—Ä–µ–∫—Ç–∏—Ä–æ–≤–∫–∞ –∑–Ω–∞–∫–∞ –≠—Ç–æ—Ç –±–ª–æ–∫ —è–≤–ª—è–µ—Ç—Å—è –æ—Å–Ω–æ–≤–æ–ø–æ–ª–∞–≥–∞—é—â–∏–º –≤–æ –º–Ω–æ–≥–∏—Ö –¶–û–° –∏ —Ü–∏—Ñ—Ä–æ–≤—ã—Ö —Å–∏—Å—Ç–µ–º–∞—Ö, –∏ —Ç–∞ –∂–µ —Å—Ç—Ä—É–∫—Ç—É—Ä–∞ –º–æ–∂–µ—Ç –±—ã—Ç—å –ª–µ–≥–∫–æ —Ä–∞—Å—à–∏—Ä–µ–Ω–∞ –¥–ª—è: –°–æ –∑–Ω–∞–∫–æ–º–æ–≤—ã–º –Ω–∞–∫–æ–ø–ª–µ–Ω–∏–µ–º –î—Ä–æ–±–Ω—ã–º –Ω–∞–∫–æ–ø–ª–µ–Ω–∏–µ–º –¶–û–° —Å —Ñ–∏–∫—Å–∏—Ä–æ–≤–∞–Ω–Ω–æ–π —Ç–æ—á–∫–æ–π –ö–æ–Ω–≤–µ–π–µ—Ä–∞–º–∏ MAC (—É–º–Ω–æ–∂–µ–Ω–∏–µ-–Ω–∞–∫–æ–ø–ª–µ–Ω–∏–µ) –∏ —Ç.–¥. –¶–∏—Ñ—Ä–æ–≤—ã–º–∏ —Ñ–∏–ª—å—Ç—Ä–∞–º–∏ –Ø–¥—Ä–∞–º–∏ –ë–ü–§/–û–ë–ü–§ –ú–æ–¥—É–ª—è—Ç–æ—Ä–∞–º–∏ –∏ –¥–µ–º–æ–¥—É–ª—è—Ç–æ—Ä–∞–º–∏ –ê–¶–ü –ë–ª–æ–∫–∞–º–∏ MAC –¥–ª—è –Ω–µ–π—Ä–æ—Å–µ—Ç–µ–π –ê–ø–ø–∞—Ä–∞—Ç–Ω–æ–π –æ–±—Ä–∞–±–æ—Ç–∫–æ–π –∞—É–¥–∏–æ –∏ –≤–∏–¥–µ–æ –õ—é–±—ã–º –ø–æ–ª—å–∑–æ–≤–∞—Ç–µ–ª—å—Å–∫–∏–º —Ç—Ä–∞–∫—Ç–æ–º –¥–∞–Ω–Ω—ã—Ö –¶–û–°, —Ç—Ä–µ–±—É—é—â–∏–º –∞—Ä–∏—Ñ–º–µ—Ç–∏–∫–∏ —Å–æ —Å–º–µ—à–∞–Ω–Ω—ã–º–∏ –∑–Ω–∞–∫–∞–º–∏ –ê–ø–ø–∞—Ä–∞—Ç–Ω–∞—è —Ä–∞–∑—Ä–∞–±–æ—Ç–∫–∞ –∏—Å–∫—É—Å—Å—Ç–≤–µ–Ω–Ω–æ–≥–æ –∏–Ω—Ç–µ–ª–ª–µ–∫—Ç–∞ (–ò–ò) –∏ –º–∞—à–∏–Ω–Ω–æ–≥–æ –æ–±—É—á–µ–Ω–∏—è (–ú–û) –ê–ø–ø–∞—Ä–∞—Ç–Ω–∞—è —Ä–∞–∑—Ä–∞–±–æ—Ç–∫–∞ –¶–û–° —Å –Ω–∏–∑–∫–∏–º —ç–Ω–µ—Ä–≥–æ–ø–æ—Ç—Ä–µ–±–ª–µ–Ω–∏–µ–º –∏ —ç—Ñ—Ñ–µ–∫—Ç–∏–≤–Ω–æ—Å—Ç—å—é –∑–∞–Ω–∏–º–∞–µ–º–æ–π –ø–ª–æ—â–∞–¥–∏ #dsp #rtl #ai #systemverilog #verilog #asics #fpga #—Å–∏–º—É–ª—è—Ü–∏—è #—ç–º—É–ª—è—Ü–∏—è #–∞–ø–ø–∞—Ä–∞—Ç–Ω–æ–µ –æ–±–µ—Å–ø–µ—á–µ–Ω–∏–µ #rtldesign #vlsijobs #vlsidesign #vlsiprojectcenters #vlsiprojects #vlsitraining #vlsicareer #vlsi #–ø–æ–ª—É–ø—Ä–æ–≤–æ–¥–Ω–∏–∫ #–ø–æ–ª—É–ø—Ä–æ–≤–æ–¥–Ω–∏–∫–æ–≤–∞—è—Ç–µ—Ö–Ω–æ–ª–æ–≥–∏—è #semiconindia2024 #–ø–æ–ª—É–ø—Ä–æ–≤–æ–¥–Ω–∏–∫–∏ #–∏–Ω–¥–∏—è #overflow #ai #aiviral #–Ω–∞—Å—ã—â–µ–Ω–∏–µ #—Ü–∏—Ñ—Ä–æ–≤–æ–π #—Ü–∏—Ñ—Ä–æ–≤–æ–π–¥–∏–∑–∞–π–Ω #–∞–ª–≥–æ—Ä–∏—Ç–º—ã #—Ö–∞–∫–∏–∞–ª–≥–æ—Ä–∏—Ç–º–æ–≤ #ùóóùó¶ùó£ #ùó¶ùòÜùòÄùòÅùó≤ùó∫ùó©ùó≤ùóøùó∂ùóπùóºùó¥ #ùó©ùóüùó¶ùóúùóóùó≤ùòÄùó∂ùó¥ùóª #ùóóùó∂ùó¥ùó∂ùòÅùóÆùóπùóóùó≤ùòÄùó∂ùó¥ùóª #ùóîùó¶ùóúùóñ #ùóôùó£ùóöùóî #ùó©ùó≤ùóøùó∂ùó≥ùó∂ùó∞ùóÆùòÅùó∂ùóºùóª #ùóõùóóùóü #ùóòùóªùó¥ùó∂ùóªùó≤ùó≤ùóøùó∂ùóªùó¥ùóüùó≤ùóÆùóøùóªùó∂ùóªùó¥ #ùóßùó≤ùó∞ùóµùóòùó±ùòÇùó∞ùóÆùòÅùó∂ùóºùóª –î–ª—è –≤—Å–µ—Ö, –≤—Å–µ—Ö, –≤—Å–µ—Ö –∏ –∫–∞–∂–¥–æ–≥–æüôè ùí≤ùí∂ùìáùìÇ ùì°ùìÆùì∞ùí∂ùìáùíπùìà, ùêÜùê≤ùêöùêß ùêÇùê°ùêöùêßùêù ùêÉùê°ùêöùê§ùêö (–≠–∫—Å–ø–µ—Ä—Ç –ø–æ –ø—Ä–æ–µ–∫—Ç–∏—Ä–æ–≤–∞–Ω–∏—é –ª–æ–≥–∏–∫–∏) (ùìú.ùíØùìÆùí∏ùíΩ - ùìúùíæùí∏ùìáùì∏ùìÆùìÅùìÆùí∏ùìâùìáùì∏ùìÉùíæùí∏ùìà –∏ ùí±ùìõùíÆùìò ùíüùìÆùìàùíæùì∞ùìÉ)