ENERGY EFFICIENT FLIP FLOP DESIGN USING VOLTAGE SCALING скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: ENERGY EFFICIENT FLIP FLOP DESIGN USING VOLTAGE SCALING в качестве 4k

У нас вы можете посмотреть бесплатно ENERGY EFFICIENT FLIP FLOP DESIGN USING VOLTAGE SCALING или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон ENERGY EFFICIENT FLIP FLOP DESIGN USING VOLTAGE SCALING в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

ENERGY EFFICIENT FLIP FLOP DESIGN USING VOLTAGE SCALING

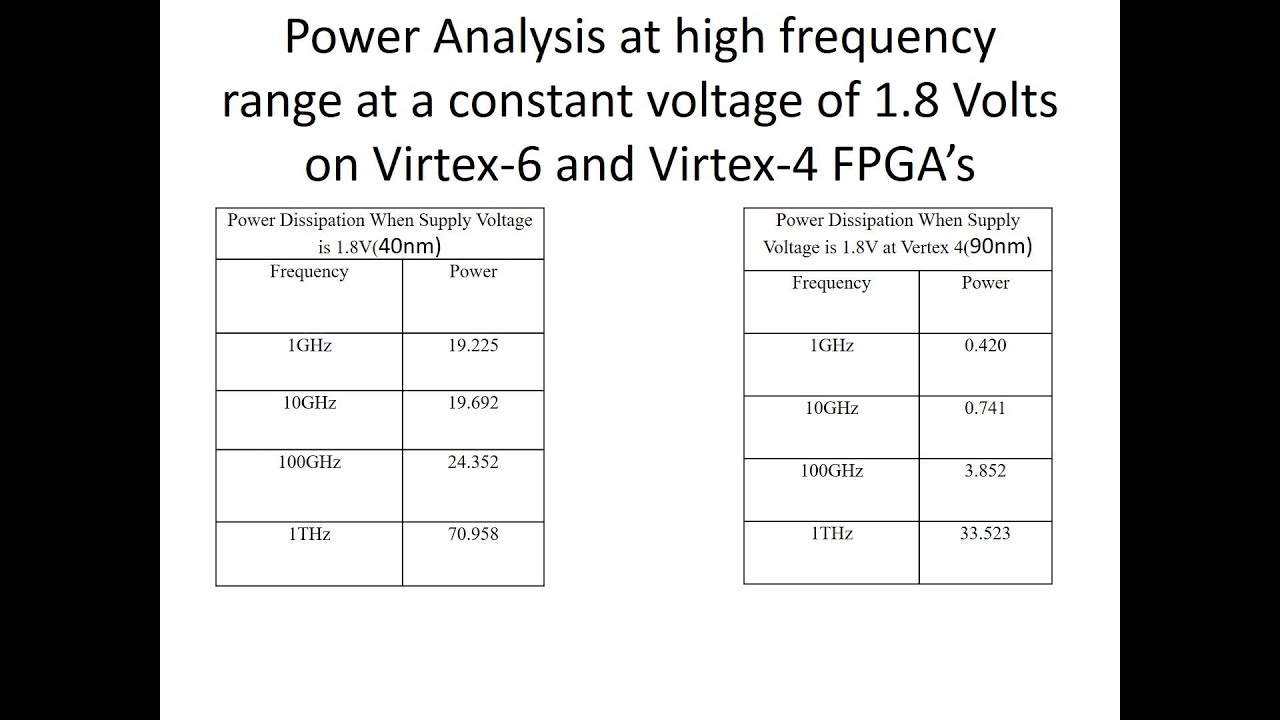

In early day of electronics, device operates with 5V voltage supply. With advancement in technology, 3.3V become the industry standard. In the era of sub-micron technology, 1.8V was standard voltage. Now, on 90nm technology onward, 1V is standard supply voltage in 65nm, and 40nm technology. Standard supply voltage is now again scaled to 0.9V for some 28nm technology. Supply voltage is expected to decrease further with upcoming technology like 14nm, 12nm, and 7nm. In this work, JK Flip-Flop is our base target design. When we scale down device operating frequencies from 1THz to 1GHz, there is 72.9% , 98.75% reduction in power dissipation on Virtex-6 FPGA and Virtex-4 FPGA respectively. When we scale down device supply voltage from 3V to 2.5V, 2V, 1.8V and 1V, there is 82.23%, 96.83%, 98.45% and 99% reduction in power dissipation respectively on Virtex-6 FPGA on 10MHz device operating frequency.

![Пожалуй, главное заблуждение об электричестве [Veritasium]](https://imager.clipsaver.ru/6Hv2GLtnf2c/max.jpg)