Gate Level Modeling | NMOS | PMOS | Verilog HDL | Learn Thought | S Vijay Murugan скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Gate Level Modeling | NMOS | PMOS | Verilog HDL | Learn Thought | S Vijay Murugan в качестве 4k

У нас вы можете посмотреть бесплатно Gate Level Modeling | NMOS | PMOS | Verilog HDL | Learn Thought | S Vijay Murugan или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Gate Level Modeling | NMOS | PMOS | Verilog HDL | Learn Thought | S Vijay Murugan в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Gate Level Modeling | NMOS | PMOS | Verilog HDL | Learn Thought | S Vijay Murugan

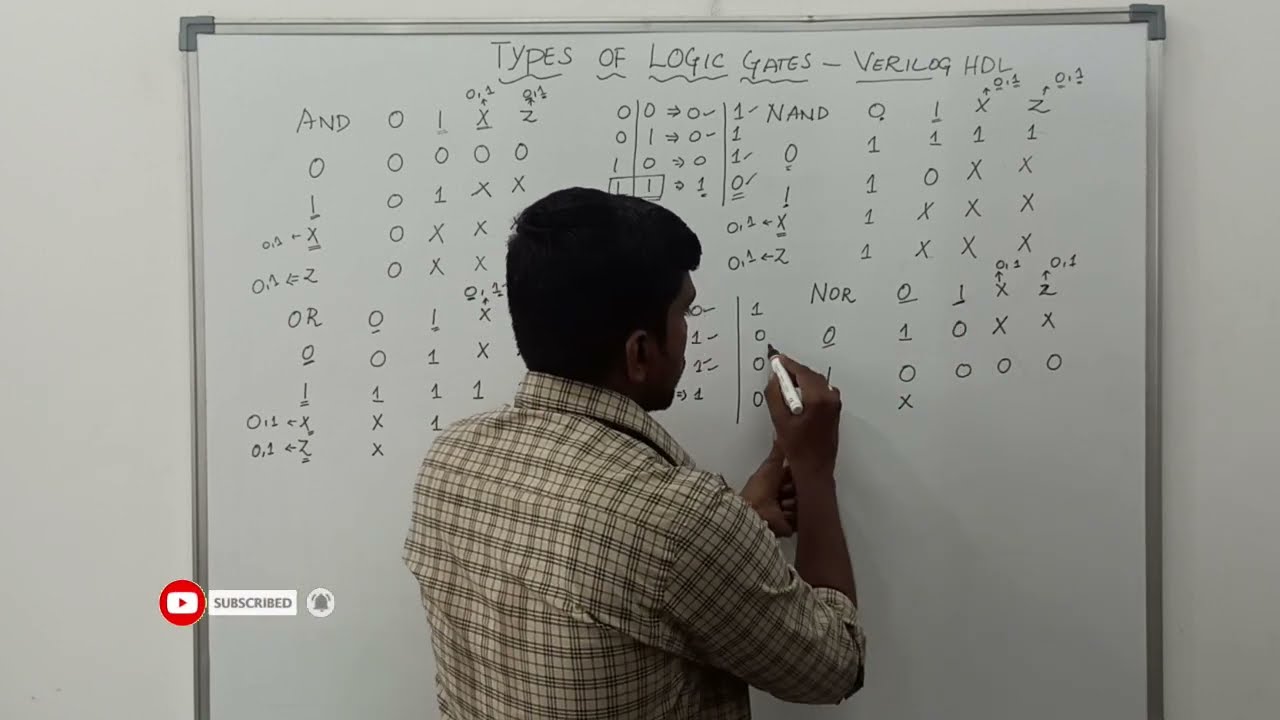

This video help to learn MOS gate and its operation with truth table explanations. #Learnthought #veriloghdl #verilog #vlsidesign #veriloglabprograms #veriloglabexperiments #verilogtutorial #verilogprogramconcepts #verilogbeginners • Building a 4-Bit Ripple Carry Adder: Step-... - 4Bit Ripple Carry Adder Verilog Program • Delay Model in Verilog HDL | VLSI Design |... - Types of delay Model • Gate Delay in Verilog | VLSI Design | S VI... - Gate Delay Model • Relational, Equality and Bitwise operator ... - Relational, Equality and bitwise Operator • Arithmetic & Logical Operators in Verilog ... - Arithmetic and Logical Operators • Reduction, Shift, Concatenation and Replic... - Reduction, Shift, Concatenation and Replication Operators • Design a Verilog Code for 2 to 4 Decoder |... - 2to4 Decoder Verilog Program • Design of 8 to 3 Encoder Using Verilog HDL... - Design 8to3 Encoder using Verilog HDL program • Comparison of Functions & Task in Verilog... - Difference between Function & Task • Design of ALU using Verilog | VLSI Design ... - How to design ALU using Verilog HDL Program • Verilog code for Half Subtractor / Learn T... - Verilog Program for Half Subtractor • Design of 8 to 3 Encoder Using Verilog HDL... - Design 8to3 Encoder using Verilog HDL Program • Design a Verilog Code for 2 to 4 Decoder |... - Verilog Program for 2 to 4 Decoder • Building a 4-Bit Ripple Carry Adder: Step-... - 4 Bit Ripple Carry Adder Verilog HDL Program • Verilog HDL PROGRAM | Full Adder | Gate Le... - Verilog HDl Program for Full Adder Gate Level Modeling • 4 to 1 MUX Verilog Code using Gate Level M... - Verilog HDL program for 4 to 1 Mux • Built in Gate Primitives in Verilog / Lea... - Built in Gate Primitives • Design of 4 bit Comparator || Verilog HDL ... - 4 Bit Comparator verilog HDL Program • Binary to Gray Code using Verilog || Learn... - Binary to gray code conversion verilog HDL Program • How to design 4 Bit Ripple Carry Counter u... - 4 Bit Ripple Carry Counter Verilog HDL Program • Realization of D_FF and implement with Ver... - Verilog HDL Code to Realize D-FF • Bitwise Operator in Verilog HDL || S VIJAY... - Verilog HDL Bitwise Operator • How to Express Numbers in Verilog HDL || L... - How to Express Number System • Binary to Gray Code Converter using Behavi... - Binary to Gray Code Converter • How to Write Verilog code for JK FF Using ... - JK FF Verilog HDL Code Using Case Statement • How to Write Verilog HDL Code for JK FF Us... - Verilog HDL Code for JK FF Gate Level Modeling • How to Write Verilog Code for SR FF using ... - SR FF using Gate Level Modeling • How to design and Write Verilog code for C... - Carry LOOK Ahead Adder • How to Write Half Adder Program using Beha... - Half Adder - Behavioral Modeling • How to write Half Subtractor Program Using... - Half Subtractor Using Behavioral Modeling • How to write Full _ Adder Program Using Ca... - Full _ Adder Using Case Statement • if else, if elseif and CASE Statement in ... - Difference between if else, if elseif and CASE Statement • What is D Latch & DFF? // Verilog HDL // L... - What is D Latch & DFF? • Difference between D latch and DFF // Veri... - Difference between D latch and DFF • Master Verilog Basics: Comments, Whitespac... - Lexical Conventions // Comment // Whitespace // Operators • Verilog Tutorial: Identifier, Keywords, Nu... - Lexical Conventions // Identifier, Keywords, Number Specification, Escaped Identifier • Design an 8X1 Multiplexer using Behavioral... - 8:1 Multiplexer using behavioral Modeling • Design a 1:4 De-multiplexer using Behavior... - 1:4 DEMULTIPLEXER BEHAVIORAL MODEL PROGRAM • How to Write 2 to 4 Decoder Verilog HDL Pr... - How to Write 2 to 4 Decoder Verilog HDL Program // Behavioral Model • Wire vs Reg - Beginners Must Know This Tri... - Syntax for wire Vs Reg // Verilog HDL • Verilog Vs Software Language // Verilog HD... - Verilog Vs Software Language // Verilog HDL • Verilog Vs C Language | Learn Thought | S ... - Verilog Vs C Language | Difference between Verilog and C | Verilog • Blocking and Non Blocking Assignments in V... - Blocking and Non Blocking Assignments | Verilog HDL • Data Types // Verilog HDL // S Vijay Murug... - Verilog Data Types // Verilog HDL • Types of Logic Gates in Verilog HDL || Log... - Verilog HDL Types of Logic Gates || Logic Input 0,1,X,Z • The Fundamentals of BUF and NOT Gate: An I... - BUF / NOT Gate | Gate Level Modeling • What is BUFIF and NOTIF? | Gate Level Mode... - BUFIF / NOTIF | Gate Level Modeling | Types of Logic Gates • Verilog code for Half Subtractor / Learn T... - Verilog Program for Half Subtractor • Design of 8 to 3 Encoder Using Verilog HDL... - Design 8to3 Encoder using Verilog HDL Program • Design a Verilog Code for 2 to 4 Decoder |... - Verilog Program for 2 to 4 Decoder • Building a 4-Bit Ripple Carry Adder: Step-... - 4 Bit Ripple Carry Adder Verilog HDl Program • Verilog HDL PROGRAM | Full Adder | Gate Le... - Verilog HDl Program for Full Adder Gate Level Modeling • 4 to 1 MUX Verilog Code using Gate Level M... - Verilog HDL program for 4 to 1 Mux • Built in Gate Primitives in Verilog / Lea... - Built in Gate Primitives • Design of 4 bit Comparator || Verilog HDL ... - 4 Bit Comparator verilog HDL Program • Binary to Gray Code using Verilog || Learn... - Binary to gray code conversion verilog HDL Program • How to design 4 Bit Ripple Carry Counter u... - 4 Bit Ripple Carry Counter Verilog HDL Program • Realization of D_FF and implement with Ver... - Verilog HDL Code to Realize D-FF • Bitwise Operator in Verilog HDL || S VIJAY... - Verilog HDL Bitwise Operator • How to Express Numbers in Verilog HDL || L... - How to Express Number System • Binary to Gray Code Converter using Behavi... - Binary to Gray Code Converter • How to Write Verilog code for JK FF Using ... - JK FF Verilog HDL Code Using Case Statement • How to Write Verilog HDL Code for JK FF Us... - Verilog HDL Code for JK FF Gate Level Modeling • How to Write Verilog Code for SR FF using ... - SR FF using Gate Level Modeling