IO pad placement | .io file writing | pad placement in Physical design flow скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: IO pad placement | .io file writing | pad placement in Physical design flow в качестве 4k

У нас вы можете посмотреть бесплатно IO pad placement | .io file writing | pad placement in Physical design flow или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон IO pad placement | .io file writing | pad placement in Physical design flow в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

IO pad placement | .io file writing | pad placement in Physical design flow

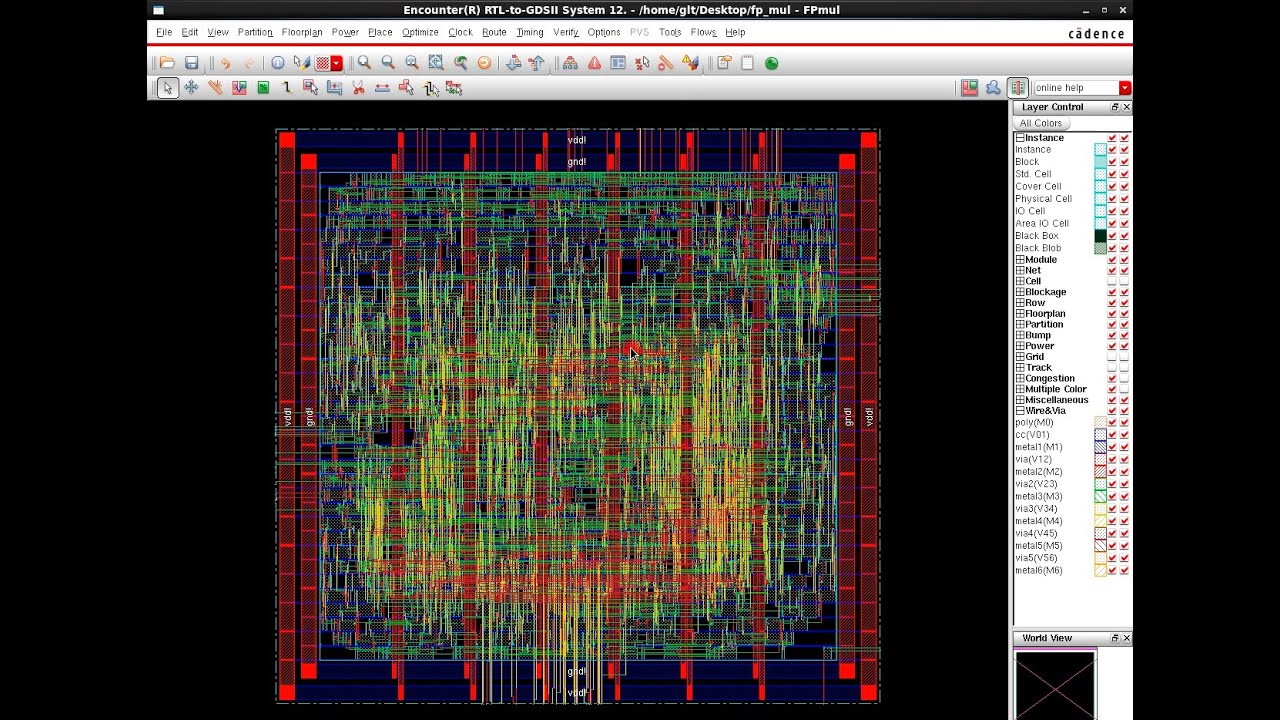

In this session, we will will discuss and demonstarate about how to write .io file which is used to io pad placement in physical design. How to use, and where to use. Step by step writing way of .io file has been explained using an example. After this session you will be able to plan your own io pads, and ou can write .io file for your design I recoment to watch our RTL-to-GDSII flow of video series, there are total 10 sessions. We have covered all the stages of ASIC design using EDA tools demonstration and also the basic theories. Part-wise descriptions of the different session and the link of videos are as follow. 1. Session-1: Overview of RTL to GDSII flow | Basic terms in the flow Video link: • RTL to GDSII flow | Basic terminology used... 2. Session-2: Flow in EDA tool's perspective | Different EDA tools | various files Video link: • ASIC Flow and EDA tools | Various files us... 3. Session-3: Functional verification of RTL | using Synopsys VCS | VCS demo Video link: • RTL Design & Simulation | Synopsys VCS Tut... 4. Session-4: Logic Synthesis flow | RTL to gate-level netlist | Design compiler Video link: • Logic Synthesis flow | RTL Synthesis flow ... 5. Session-5: Logic Synthesis | Design Compiler | Command-line | gate level netlist Video link: • Logic Synthesis of RTL | Synopsys Design C... 6. Session-6: Logic Synthesis | Design Compiler | GUI Mode| design_vision Video link: • Logic Synthesis in Design Compiler | GUI M... 7. Session-7: Logic Equivalence Check using Formality |S8| RTL-to-GDSII flow | Formality tutorial Video link: • Logic Equivalence Check | Synopsys Formali... 8. Session-8: Physical Design Flow | PnR flow |RTL-to-GDSII flow | innovus flow Video link: • Physical Design Flow | PnR flow | RTL-to-G... 9. Session-9: Design Import | Physical Design |RTL-to-GDSII flow | innovus tools tutorial Video link: • Design Import | Cadence Innovus | GUI of I... 10.Session-10: Place and Route in Cadence Innovus | full PnR flow | Cadence Innovus demo Video link: • Place and Route in Cadence Innovus | full... ============================== Connect with us All on one page: https://www.teamvlsi.com/p/contact_8.... Blog: https://www.teamvlsi.com Facebook Page: / teamvlsi WhatsApp Group: https://chat.whatsapp.com/C6etLHR6oAf... Telegram Group: https://t.me/teamvlsi (Or search team VLSI on telegram) Email: teamvlsi2014@gmail.com ============================== #padfram #ioPadPlacement #.iofile

![PD Lec 17 – Планировка этажей и размещение ввода-вывода [часть 3] | СБИС | Физическое проектирование](https://imager.clipsaver.ru/YcwY1PH31qg/max.jpg)