Testbench for Sequential Circuits | Flip-Flops & Synchronous Counters | Verilog Tutorial скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Testbench for Sequential Circuits | Flip-Flops & Synchronous Counters | Verilog Tutorial в качестве 4k

У нас вы можете посмотреть бесплатно Testbench for Sequential Circuits | Flip-Flops & Synchronous Counters | Verilog Tutorial или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Testbench for Sequential Circuits | Flip-Flops & Synchronous Counters | Verilog Tutorial в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Testbench for Sequential Circuits | Flip-Flops & Synchronous Counters | Verilog Tutorial

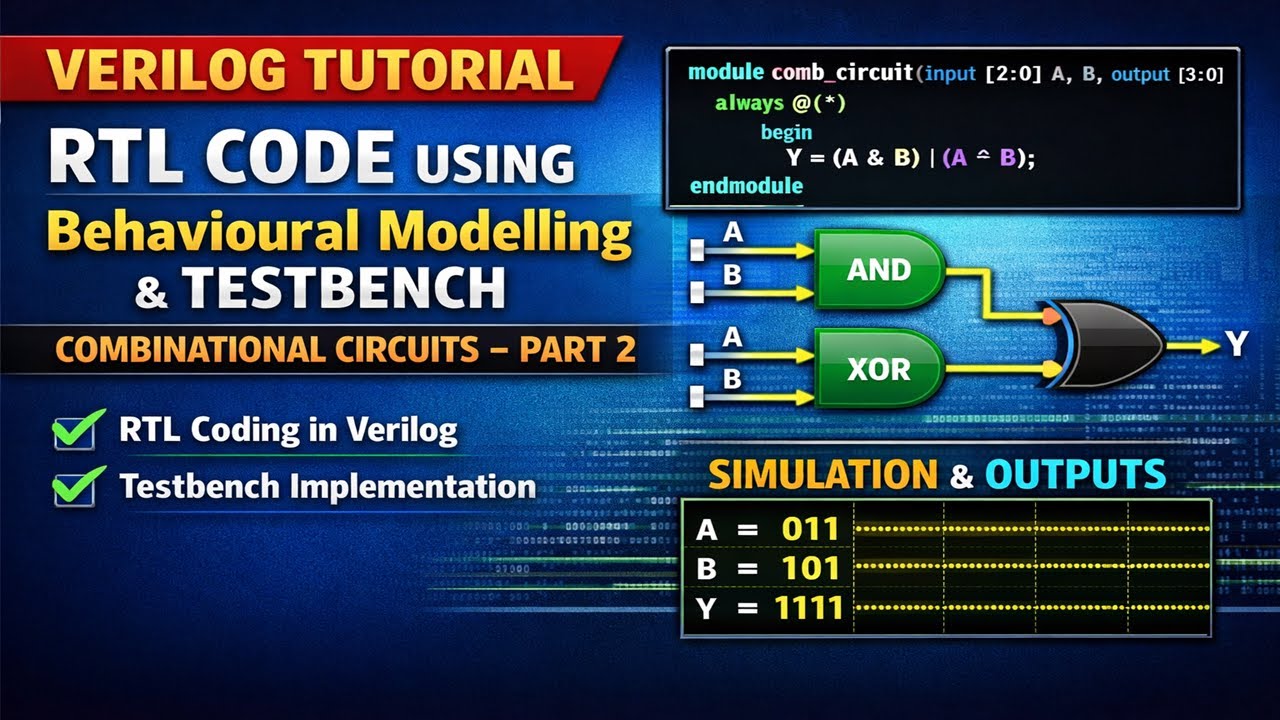

🎯 Master Testbench Writing for Sequential Circuits | Complete Verilog/SystemVerilog Tutorial Learn how to write professional testbenches for sequential circuits including Flip-Flops, Counters, and Finite State Machines. This comprehensive tutorial covers industry-standard verification techniques used in VLSI and FPGA design. 📌 What You'll Learn: ✅ Testbench fundamentals for sequential circuits ✅ Clock generation and timing control ✅ Reset strategies (synchronous vs asynchronous) ✅ D, JK, T, and SR Flip-Flop verification ✅ Synchronous counter testbenches (Binary, Up-Down, Ring, Johnson) ✅ FSM (Finite State Machine) verification ✅ Timing verification and assertions ✅ Waveform analysis in simulation tools ✅ Self-checking testbenches ✅ Code coverage and functional coverage 🔥 Topics Covered: ⏱️ 00:00 - Introduction to Sequential Circuit Testing ⏱️ 02:30 - Clock Generation Techniques ⏱️ 05:45 - Reset Methodology ⏱️ 08:20 - D Flip-Flop Testbench ⏱️ 12:15 - JK Flip-Flop Testbench ⏱️ 16:30 - Counter Testbenches (Binary, Up-Down) ⏱️ 22:00 - Ring & Johnson Counter Verification ⏱️ 27:45 - FSM Testbench Design ⏱️ 33:20 - Timing Checks & Assertions ⏱️ 38:10 - Best Practices & Common Pitfalls ⏱️ 42:00 - Conclusion & Next Steps 💻 Complete Code Available: 📁 GitHub Repository: [Your Link] 📄 PDF Notes: [Your Link] 🔗 Blog Post: [Your Link] 🎓 Perfect For: M.Tech/B.Tech VLSI students FPGA/ASIC design engineers Digital design enthusiasts IEEE project developers Verification engineers Hardware description language learners 🛠️ Tools Used: ModelSim / QuestaSim Xilinx Vivado SystemVerilog / Verilog GTKWave (Open Source) 📚 Related Videos: 🔗 Combinational Circuit Testbenches: [Link] 🔗 Advanced SystemVerilog OOP: [Link] 🔗 UVM Verification Basics: [Link] 🔗 State Machine Design Tutorial: [Link] 💡 Key Concepts: #SystemVerilog #Verilog #VLSI #FPGA #DigitalDesign #Testbench #FlipFlops #Counters #FSM #RTLDesign #DesignVerification #ASICDesign #HardwareDescription #ECE #ElectricalEngineering 📖 Prerequisites: Basic Verilog/SystemVerilog knowledge Understanding of sequential circuits Familiarity with digital logic design 🎯 Learning Outcomes: By the end of this tutorial, you'll be able to: ✓ Write production-quality testbenches for any sequential circuit ✓ Implement industry-standard verification techniques ✓ Debug timing issues in sequential designs ✓ Create self-checking automated testbenches ✓ Apply assertions for comprehensive verification ✓ Analyze simulation waveforms effectively 📞 Connect With Me: 🔗 LinkedIn: [Your Profile] 🐦 Twitter: [Your Handle] 💼 GitHub: [Your Repository] 📧 Email: [Your Email] 🌐 Website: [Your Website] 👍 If you found this helpful: Like this video Subscribe for more VLSI tutorials Share with fellow engineers Comment your questions below Enable notifications 🔔 💬 Questions or Suggestions? Drop them in the comments! I read and respond to every comment. 📚 Recommended Resources: "Digital Design and Computer Architecture" by Harris & Harris "SystemVerilog for Verification" by Chris Spear IEEE Std 1800-2017 (SystemVerilog) 🎓 Course Series: This video is part of our complete Digital Design Verification series: 1️⃣ Combinational Circuit Testbenches 2️⃣ Sequential Circuit Testbenches (This Video) 3️⃣ Advanced Verification Techniques 4️⃣ UVM Fundamentals 5️⃣ Assertion-Based Verification ⭐ Timestamps for Quick Navigation: Use the timeline above to jump to specific topics! #VerilogTutorial #DigitalElectronics #ChipDesign #HardwareVerification #ECEProjects #MTechVLSI #FPGAProgramming #RTLVerification #SemiconductorDesign #LearnVerilog --- © 2024 [Your Channel Name] | All Rights Reserved Subscribe for weekly VLSI & Digital Design tutorials!