4 - Data Flow vs. Structural Modeling | verilog скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: 4 - Data Flow vs. Structural Modeling | verilog в качестве 4k

У нас вы можете посмотреть бесплатно 4 - Data Flow vs. Structural Modeling | verilog или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон 4 - Data Flow vs. Structural Modeling | verilog в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

4 - Data Flow vs. Structural Modeling | verilog

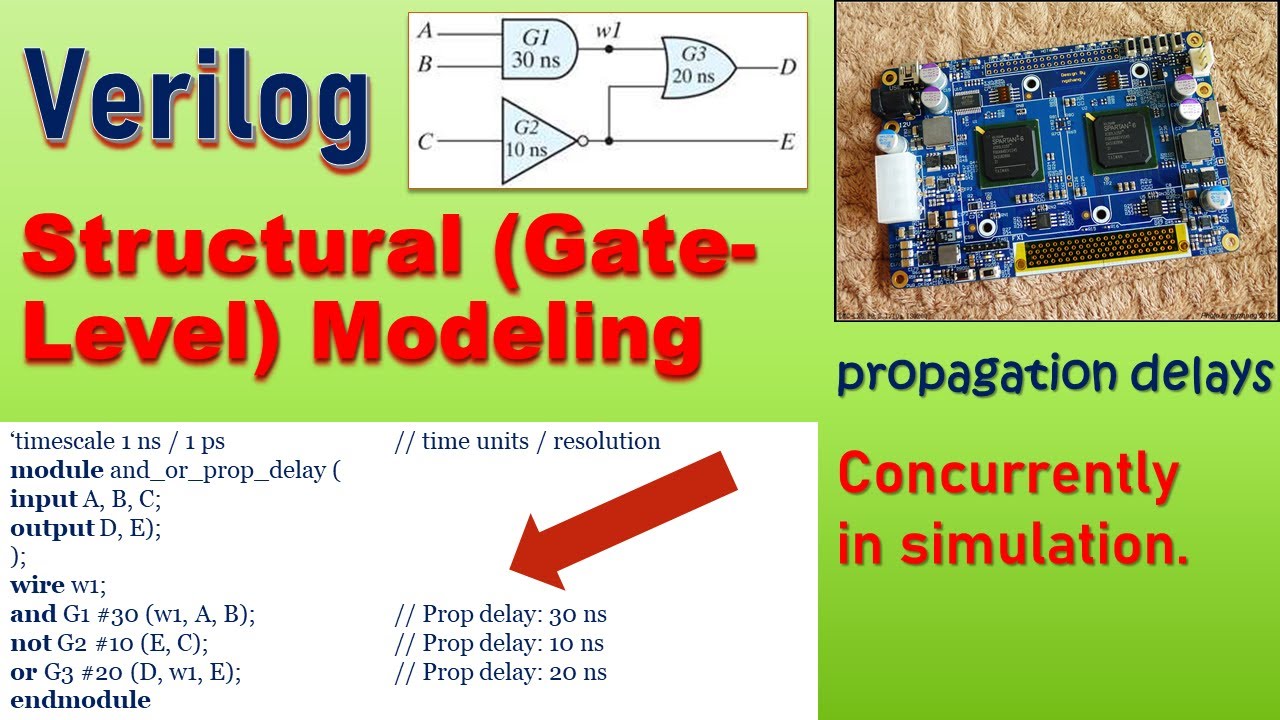

Welcome back to our Verilog tutorial series! In this video, we continue our exploration of Verilog, a powerful hardware description language used to model and describe digital electronics components. We start by revisiting data flow modeling, where we describe circuits using Boolean expressions to determine how data flows from inputs to outputs. Then, we dive into the structural (or gate-level) modeling technique, where we utilize Verilog's built-in primitives like AND, OR, and NOT gates to create more complex circuits. We also touch on propagation delay, an essential aspect of real-world circuits, and how it’s incorporated into Verilog code. By the end of this video, you'll have a solid understanding of both data flow and structural modeling techniques in Verilog, allowing you to design and simulate digital circuits effectively. Stay tuned for more as we explore behavioral modeling in future modules! 🔔 If you find this content helpful, don’t forget to like, share, and subscribe to our channel for more tutorials on Verilog and other digital design topics. Happy learning! #Verilog #DigitalDesign #HardwareDescriptionLanguage #Electronics #DataFlowModeling #StructuralModeling #GateLevelModeling #PropagationDelay #DigitalCircuits

![Почему работает теория шести рукопожатий? [Veritasium]](https://imager.clipsaver.ru/ggI1xKzoANs/max.jpg)