HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video в качестве 4k

У нас вы можете посмотреть бесплатно HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

HDL Coder Clock Rate Pipelining, Part 2: Optimization - MATLAB and Simulink Video

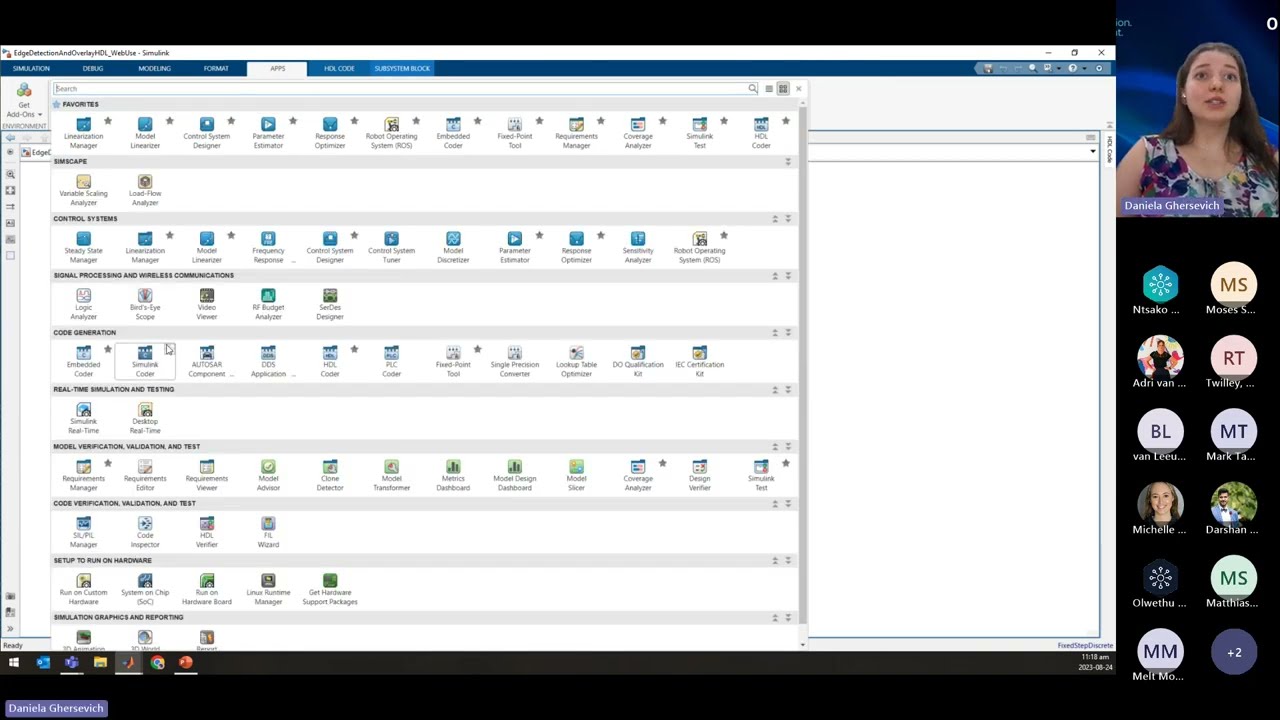

This is part two of a two-part series on clock rate pipelining. Get a Trial of Simulink: https://goo.gl/ScEHEe Get a Trial of MATLAB: https://goo.gl/C2Y9A5 Learn more about HDL coder: https://goo.gl/vqxP3r This is part two of a two-part series on clock rate pipelining, using a field-oriented control (FOC) design to illustrate: How resource sharing reduces FPGA DSP slice usage at the cost of extra latency How clock rate pipelining works with resource sharing to minimize the latency of inserted logic How to further optimize the latency of the FOC design Part one of this series provides an introductory overview on: How Simulink® sample rates map to FPGA clock rates How to use HDL Coder™ oversampling together with clock rate pipelining to control optimization