Comparative Analysis of Simulation Techniques Scan Compression and Internal Scan скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Comparative Analysis of Simulation Techniques Scan Compression and Internal Scan в качестве 4k

У нас вы можете посмотреть бесплатно Comparative Analysis of Simulation Techniques Scan Compression and Internal Scan или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Comparative Analysis of Simulation Techniques Scan Compression and Internal Scan в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Comparative Analysis of Simulation Techniques Scan Compression and Internal Scan

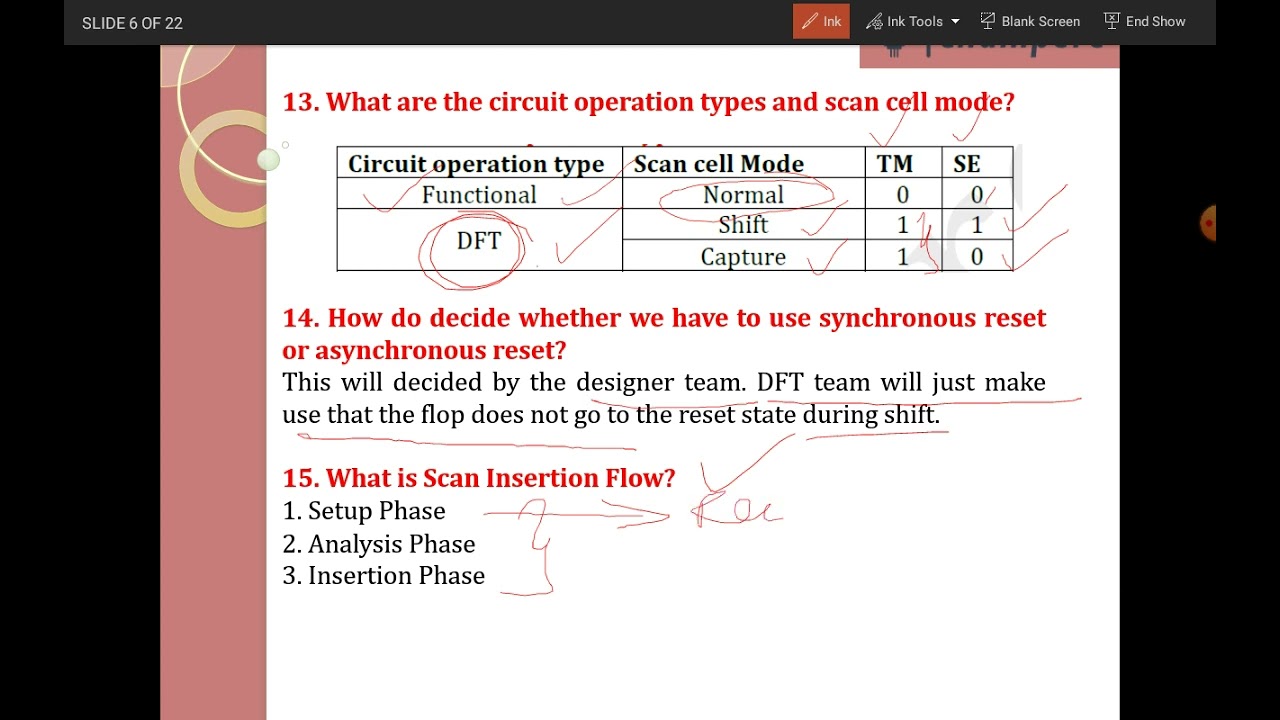

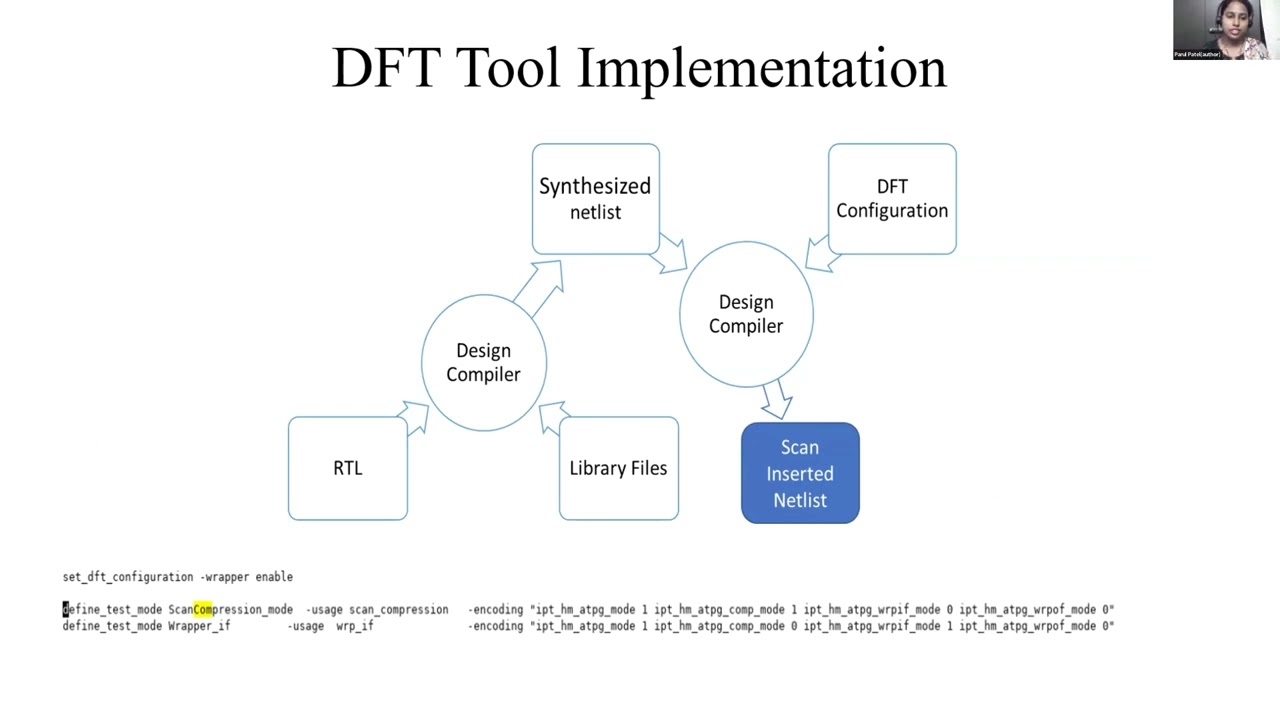

Comparative Analysis of Simulation Techniques: Scan Compression and Internal Scan Authors Parul Patel1, Arvind Rajawat1 and Pooja Jain2, 1Maulana Azad National Institute of Technology Bhopal, India, 2Automotive and Discrete group STMicroelectronics Private Limited Greater Noida, India Abstract With advancement in technology, the feature size of transistors is shrinking and the transistor count in a circuit design is exponentially increasing. As a result, it is hard to control and observe internal nodes leading to complexity in locating and debugging faults specially for sequential circuits. Design for Testability (DFT) provides a way for fault detection of the circuit under test in less simulation duration with little increase in area. Many techniques are proposed under DFT for pattern simulation. In this paper, we have compared two such pattern simulation techniques namely scan compression and internal scan. The experiment is performed on different benchmark circuits, it is observed the simulation time is significantly reduced with increased coverage and a little area overhead. Keywords DFT, Scan Compression, Internal Scan Full Text : https://ijcionline.com/paper/12/12523... Abstract URL: https://ijcionline.com/abstract/12523... Volume URL : https://ijcionline.com/volume/v12n5 #dftf #scan #compression