Using the Integrated Logic Analyzer to Debug Versal Designs With AI Engines скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Using the Integrated Logic Analyzer to Debug Versal Designs With AI Engines в качестве 4k

У нас вы можете посмотреть бесплатно Using the Integrated Logic Analyzer to Debug Versal Designs With AI Engines или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Using the Integrated Logic Analyzer to Debug Versal Designs With AI Engines в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Using the Integrated Logic Analyzer to Debug Versal Designs With AI Engines

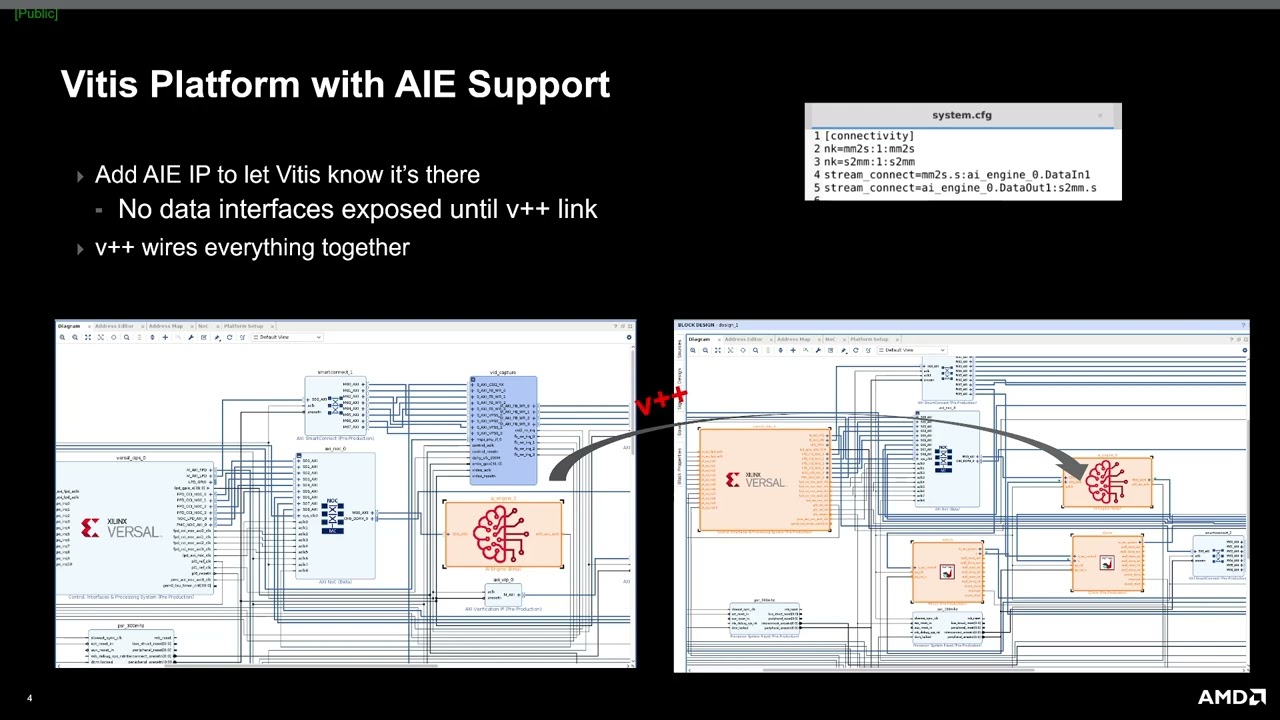

0:00 Introduction 1:10 Chipscope/ILA demonstration 3:45 New aspects of the Vitis/Versal flow 4:27 Compute domains 6:10 New host-target interface hardware 10:45 Cross-domain debugging strategies 11:18 Adding the ILA in Versal 15:00 Adding the ILA in Vivado 19:30 Adding the ILA in Vitis 22:30 Running the ILA 25:35 Running the Vitis Debugger with the ILA 27:10 ILA features useful for debugging AIE interfaces 29:05 If you want to learn more 29:57 Summary This video demonstrates how the ChipScope Integrated Logic Analyzer (ILA) can be used to debug Versal AI Engines. Discussion and demos cover the debug hardware, tools, and techniques. The intended audience is hardware/software engineers debugging prototype Versal designs in hardware. A working knowledge of the ChipScope ILA is presumed; the focus is how to extend that tool into the Vitis and Versal design process. REFERENCED DOCUMENTS VCK190 Evaluation Board User Guide (UG1366) Versal ACAP AI Engine Architecture Manual (AM009) Vivado Design Suite User Guide: Programming and Debugging (UG908) Vitis Unified Software Platform Documentation: Application Acceleration Development (UG1393) Integrated Logic Analyzer (ILA) with AXI4-Stream Interface LogiCORE IP Product Guide (PG357) Xilinx Versal ACAP AI Engine Programming Environment User Guide (UG1076) REFERENCED LINKS VCK190 Product Page https://www.xilinx.com/products/board... Versal Custom Thin Platform https://github.com/Xilinx/Vitis-Tutor...