set_case_analysis Explained for Scan DFF | Functional vs Scan Mode | STA Interview Guide скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: set_case_analysis Explained for Scan DFF | Functional vs Scan Mode | STA Interview Guide в качестве 4k

У нас вы можете посмотреть бесплатно set_case_analysis Explained for Scan DFF | Functional vs Scan Mode | STA Interview Guide или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон set_case_analysis Explained for Scan DFF | Functional vs Scan Mode | STA Interview Guide в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

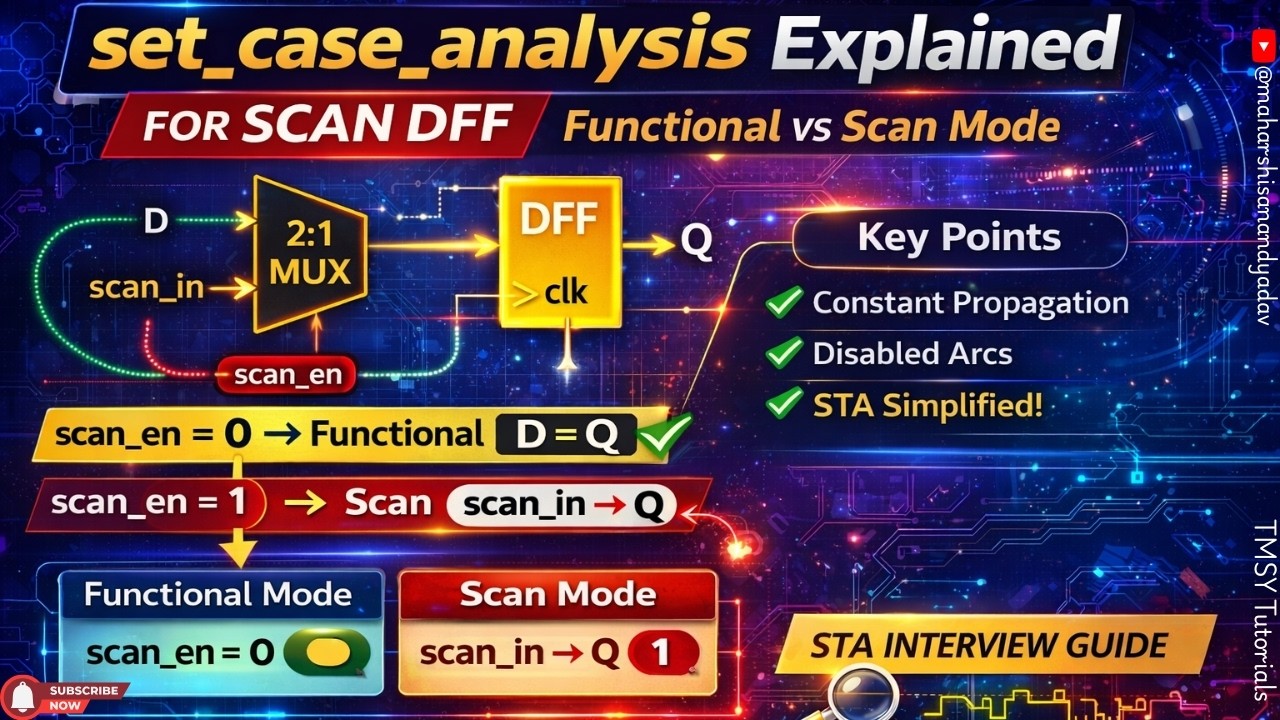

set_case_analysis Explained for Scan DFF | Functional vs Scan Mode | STA Interview Guide

https://amzn.to/4aB3xiQ 00:00 Introduction – What is set_case_analysis? 00:50 Scan DFF Structure (2:1 MUX + D Flip-Flop) 01:28 Input Signals Explained (D, scan_in, scan_en) 01:45 How scan_en Selects Functional vs Scan Mode 02:40 Functional Mode (scan_en = 0) – Timing Behavior 03:49 Writing set_case_analysis for Functional Mode 05:21 Disabled Timing Arcs in Functional Mode 06:15 Scan Mode (scan_en = 1) – Timing Behavior 06:36 Writing set_case_analysis for Scan Mode 07:32 Disabled Timing Arcs in Scan Mode 08:01 Final Summary – Functional vs Scan Mode Comparison In this video, we clearly explain the set_case_analysis command used in Static Timing Analysis (STA) for Scan D Flip-Flops (Scan DFFs). If you are working in STA, Synthesis, or DFT, this concept is extremely important — especially for interviews in companies like AMD, Qualcomm, Synopsys, Intel, etc. We cover: • Scan DFF structure (2:1 MUX + DFF) • Functional mode vs Scan mode timing • How set_case_analysis works internally • Constant propagation inside timing engine • Disabled timing arcs explanation • Interview-ready answers • Crosstalk impact discussion • Real TCL examples Example Commands Covered: set_case_analysis 0 [get_ports scan_en] set_case_analysis 1 [get_ports scan_en] After watching this video, you will clearly understand: ✔ Why we use case analysis ✔ How STA tools remove false paths ✔ How mux-based scan DFF timing is handled ✔ How to confidently explain in interviews This tutorial is perfect for: • STA Engineers • Physical Design Engineers • Synthesis Engineers • VLSI Interview Preparation • Digital Design learners If you're preparing for VLSI interviews or working on scan timing closure, this video will make the concept crystal clear. 🏷 Tags (Comma Separated) set_case_analysis, scan dff, static timing analysis, STA tutorial, scan enable timing, mux based dff, scan chain timing, functional mode vs scan mode, case analysis sta, dft timing, synthesis timing, VLSI interview questions, RTL to gate level, timing arc disable, constant propagation sta, scan shift timing, digital VLSI, ASIC design, TCL commands STA, setup hold analysis ✨ Stay Connected with Me: 👉 Become a TMSY Community Member: / @maharshisanandyadav 💼 LinkedIn → / t-maharshi-sanand-yadav 🎓 Udemy Course → https://www.udemy.com/course/digital-... 📸 Instagram → / vlsi.tmsy.tutorials 🎥 YouTube → / @maharshisanandyadav 📂 More Learning Playlists: 🔹 Standard Cell Characterization → • standard cell characterization 🔹 STA → • STA || Static Timing Analysis 🔹 Synthesis and STA → • Synthesis and STA 🔹 Verilog Codes → • Verilog HDL Complete Course | Digital Logi... ✨ Hashtags for reach: #VLSI #PowerCharacterization #StaticPower #SubthresholdLeakage #CMOS #LowPowerDesign #VLSIDesign #ASIC #SoC #ICDesign #EDATools #Cadence #Synopsys #Semiconductors #ChipDesign #PhysicalDesign #StandardCell #LibraryCharacterization #STA #Synthesis #EDA #ElectronicsEngineering #Microelectronics #SemiconductorDesign #CMOSDesign #DigitalDesign #ICFabrication #VLSITutorial #Transistor #MOSFET #GateLeakage #CircuitDesign #AnalogDesign #DigitalElectronics #Verilog #SystemVerilog #RTLDesign #RTLtoGDS #DesignFlow #ASICDesignFlow #ICLayout #LogicDesign #ElectronicsTutorial #ChipManufacturing #VLSIProjects #VLSIInterview #PlacementPreparation #ChipFabrication #TechSemiconductors #PowerOptimization #LeakageCurrent #TransistorLeakage #ProcessTechnology #FinFET #NanometerTechnology #28nm #16nm #7nm #5nm #3nm #EDAsoftware #StaticTimingAnalysis #TimingClosure #PlaceAndRoute #ClockTreeSynthesis #ClockGating #PowerGating #MultiVth #CMOSInverter #ICTesting #ChipVerification #SoCDesign #ASICVerification #PhysicalVerification #LayoutVerification #DFT #DesignForTest #VLSITraining #VLSICourse #VLSILearning #ECE #EEE #MOSCircuits #TransistorTheory #SemiconductorPhysics #ElectronicDevices #TechnologyScaling #PowerAnalysis #SignalIntegrity #NoiseAnalysis #OnChipPower #LeakageReduction #LowPowerVLSI #SubthresholdConduction #ThermalAnalysis #CadenceGenus #CadenceInnovus #Liberate #SynopsysPrimeTime #DesignCompiler #StaticLeakage #DynamicPower #HardwareDesign #VLSIEngineer #EDAEngineer #IntegratedCircuits #MOSFETLeakage #StandardCellLibrary #CircuitSimulation #SpiceSimulation #SpectreSimulation #ChipDesignProcess #ICDesignProcess #SemiconductorBasics #ChipFabricationProcess #SoCProjects #EDAProject #StaticAnalysis #DynamicAnalysis #Redhawk #AdvancedNodes #ClockDomainCrossing #VLSITips #Netlist #TimingOptimization #GateLevelSimulation #PostLayoutSimulation #SignalIntegrityAnalysis #TMSYTutorials #MaharshiSanandYadav