Efficient Portable Programming-Sequence Development with PSS скачать в хорошем качестве

Повторяем попытку...

Скачать видео с ютуб по ссылке или смотреть без блокировок на сайте: Efficient Portable Programming-Sequence Development with PSS в качестве 4k

У нас вы можете посмотреть бесплатно Efficient Portable Programming-Sequence Development with PSS или скачать в максимальном доступном качестве, видео которое было загружено на ютуб. Для загрузки выберите вариант из формы ниже:

-

Информация по загрузке:

Скачать mp3 с ютуба отдельным файлом. Бесплатный рингтон Efficient Portable Programming-Sequence Development with PSS в формате MP3:

Если кнопки скачивания не

загрузились

НАЖМИТЕ ЗДЕСЬ или обновите страницу

Если возникают проблемы со скачиванием видео, пожалуйста напишите в поддержку по адресу внизу

страницы.

Спасибо за использование сервиса ClipSaver.ru

Efficient Portable Programming-Sequence Development with PSS

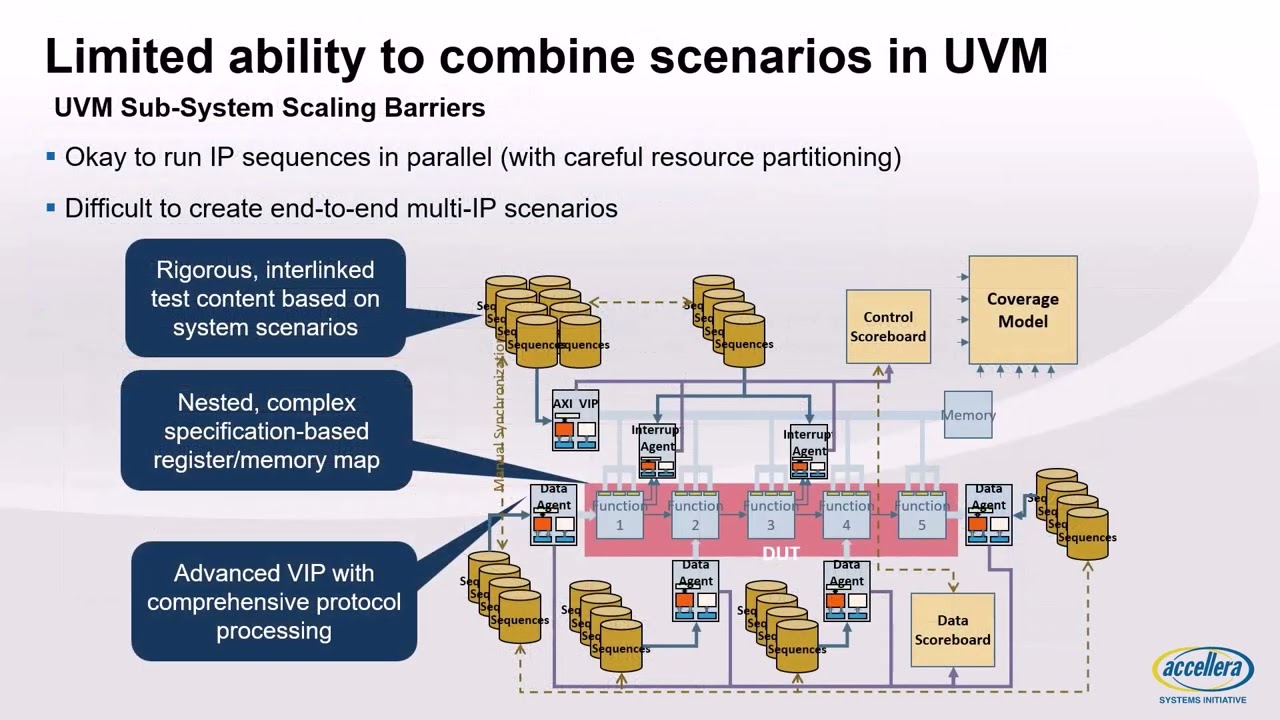

Tutorial: Efficient Portable Programming-Sequence Development with PSS Presented at DVCon U.S. 2024 by members of Accellera System Initiative Bringing an SoC-level system out of reset into an operational state involves configuring the component subsystems and IPs by properly programming hundreds or thousands of IP registers. Running behavior involves programming yet more registers and in-memory descriptors. Stake holders, including block-DV, subsystem, SoC verification, silicon bring-up teams, rely on having early access to accurate programming sequences in order to shift-left their activities. Many of these stakeholders also depend on being able to efficiently modify/adjust the programming sequences to exercise different legal configurations and operations. Current approaches to deriving bring-up sequences often require block-level teams to create some C code that captures key register-programming sequences to hand off to subsystem and SoC teams. Creating this content is an extra task that the block-level team would not normally perform, and is often deferred until late in the verification cycle. This limits the ability of subsystem and SoC teams to left-shift their activities. The programming sequences are typically highly directed, and cannot be easily modified to exercise different scenarios. Finally, because creating C-code programming sequences is disconnected from the primary work of a block-level DV team, they are at high risk of becoming outdated. This tutorial includes an overview of the PSS features in development for PSS 3.0, as well as an introduction to the PSS methodology library currently under development by the Accellera Portable Stimulus Working Group. Part 1: Agenda Tom Fitzpatrick, Siemens EDA (00:00) Part 2: PSS Motivation Adnan Hamid, Breker (1:42) Part 3: What Is PSS? Tom Fitzpatrick, Siemens EDA (19:41) Part 4: Developing Reusable Test Content at the Block Level Matthew Ballance, AMD (50:23) Part 5: Sub-system and SoC–level Testing with PSS Sergey Khaikin, Cadence (1:29:11) Part 6: Post-silicon Testing with PSS Prabhat Gupta, AMD (2:01:12) Part 7: Wrapping Up Tom Fitzpatrick, Siemens EDA (2:26:55) https://dvcon.org https://dvcon-proceedings.org https://accellera.org

![3. CS50 на русском: Лекция #3 [Гарвард, Основы программирования, осень 2015 год]](https://imager.clipsaver.ru/agdXnmEadCM/max.jpg)